# DAQ

# DAQ Hardware Overview Guide

January 2000 Edition Part Number 370097A-01

#### Worldwide Technical Support and Product Information

www.ni.com

#### **National Instruments Corporate Headquarters**

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 794 0100

#### **Worldwide Offices**

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Brazil 011 284 5011, Canada (Calgary) 403 274 9391, Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, China 0755 3904939, Denmark 45 76 26 00, Finland 09 725 725 11, France 01 48 14 24 24, Germany 089 741 31 30, Greece 30 1 42 96 427, Hong Kong 2645 3186, India 91805275406, Israel 03 6120092, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico (D.F.) 5 280 7625, Mexico (Monterrey) 8 357 7695, Netherlands 0348 433466, Norway 32 27 73 00, Poland 48 22 528 94 06, Portugal 351 1 726 9011, Singapore 2265886, Spain 91 640 0085, Sweden 08 587 895 00, Switzerland 056 200 51 51, Taiwan 02 2377 1200, United Kingdom 01635 523545

For further support information, see the *Technical Support Resources* appendix. To comment on the documentation, send e-mail to techpubs@ni.com

© Copyright 2000 National Instruments Corporation. All rights reserved.

# **Important Information**

#### Warranty

DAQ hardware is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR MEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopyring, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### Trademarks

AMUX-64T<sup>TM</sup>, CVI<sup>TM</sup>, DAQCard<sup>TM</sup>, DAQPad<sup>TM</sup>, DAQ-PnP<sup>TM</sup>, DAQ-STC<sup>TM</sup>, LabVIEW<sup>TM</sup>, National Instruments<sup>TM</sup>, ni.com<sup>TM</sup>, NI-DAQ<sup>TM</sup>, NI-DSP<sup>TM</sup>, NI-PGIA<sup>TM</sup>, PXI<sup>TM</sup>, RTSI<sup>TM</sup>, SCXI<sup>TM</sup>, and VirtualBench<sup>TM</sup> are trademarks of National Instruments Corporation.

Product and company names mentioned herein are trademarks or trade names of their respective companies.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CAN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY, COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED "SYSTEM FAILURES"). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILY INJURY AND DEATH) SHOULD NOT BE RELIANT SOLELY UPON ONE FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS. BECAUSE EACH END-USER SYSTEM IS CUSTOMIZED AND DIFFERS FROM NATIONAL INSTRUMENTS' TESTING PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS PRODUCTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

### **About This Guide**

| Conventions                     | ii  |

|---------------------------------|-----|

| MIO and AI Device Terminologyxv | i   |

| Related Documentationxv         | iii |

### Chapter 1 MIO and AI Devices

| MIO and AI Multifunction I/O Devices              | 1-1  |

|---------------------------------------------------|------|

| MIO and AI Device Analog Input                    | 1-1  |

| E Series Data Acquisition                         | 1-3  |

| E Series Data Acquisition Timing                  | 1-5  |

| E Series Data Acquisition Rates                   | 1-7  |

| MIO Device Analog Output                          | 1-7  |

| MIO Device Waveform Generation                    | 1-7  |

| E Series Waveform Generation Using Onboard Memory | 1-8  |

| E Series Digital I/O                              | 1-9  |

| E Series Counter/Timer Operation                  | 1-10 |

| E Series Programmable Frequency Output Operation  | 1-10 |

| E Series PFI Pins                                 | 1-10 |

|                                                   |      |

### Chapter 2 Lab and 1200 Devices

| Lab and 1200 Devices Analog Input                     | 2-1 |

|-------------------------------------------------------|-----|

| Lab and 1200 Devices Data Acquisition                 |     |

| Lab and 1200 Devices Data Acquisition Timing          | 2-3 |

| Lab and 1200 Devices Data Acquisition Rates           | 2-5 |

| Lab and 1200 Devices Analog Output                    | 2-5 |

| Lab and 1200 Devices Waveform Generation              | 2-6 |

| Lab and 1200 Devices Digital I/O                      | 2-6 |

| Lab and 1200 Devices Groups                           | 2-6 |

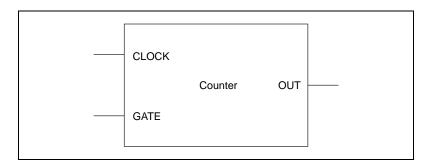

| Lab and 1200 Devices Interval Counter/Timer Operation | 2-7 |

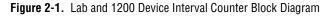

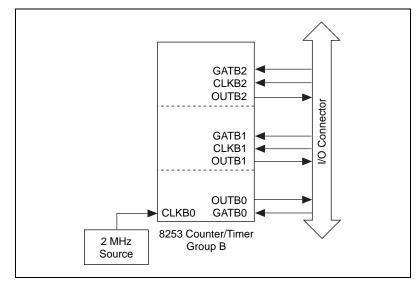

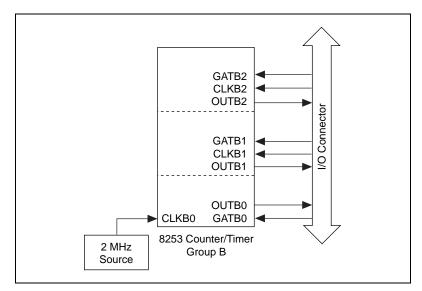

| Lab and 1200 Devices Counter/Timers                   | 2-7 |

| 1200 Device Acquisition Rate                          | 2-8 |

| DAQPad-1200 Printer Connection                        | 2-9 |

| 1200 Device Calibration                               |     |

|                                                       |     |

### Chapter 3 LPM Devices

| LPM Device Analog Input                     |  |

|---------------------------------------------|--|

| LPM Device Data Acquisition                 |  |

| LPM Device Data Acquisition Timing          |  |

| LPM Device Data Acquisition Rates           |  |

| LPM Device Digital I/O                      |  |

| LPM Device Interval Counter/Timer Operation |  |

| LPM Device Counter/Timers                   |  |

|                                             |  |

### Chapter 4 516 Devices and DAQCard-500/700 Devices

| 516 Devices and DAQCard-500/700 Analog Input                     | 4-1 |

|------------------------------------------------------------------|-----|

| 516 Devices and DAQCard-500/700 Data Acquisition                 | 4-2 |

| 516 Devices and DAQCard-500/700 Data Acquisition Timing          | 4-2 |

| 516 Devices and DAQCard-500/700 Digital I/O                      | 4-3 |

| 516 Devices and DAQCard-500/700 Interval Counter/Timer Operation | 4-4 |

| DAQCard-700 Counter/Timers                                       | 4-4 |

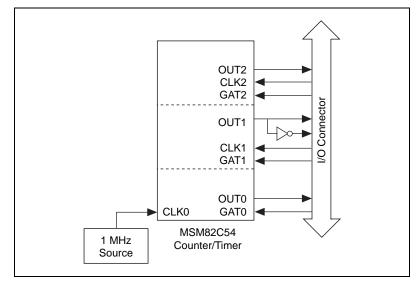

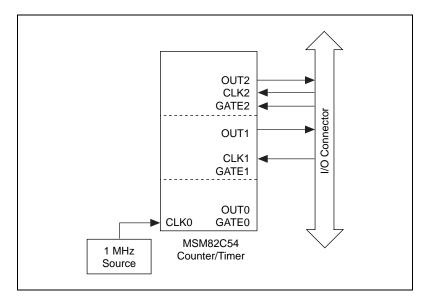

| 516 Devices and DAQCard-500 Counter/Timers                       | 4-5 |

|                                                                  |     |

### Chapter 5 AT-AO-6/10 Analog Output Devices

| AT-AO-6/10 Analog Output                 | 5-1 |

|------------------------------------------|-----|

| AT-AO-6/10 Waveform Generation           |     |

| Waveform Generation Using Onboard Memory | 5-1 |

| Hardware Restrictions for the AT-AO-6/10 | 5-2 |

| AT-AO-6/10 Digital I/O                   | 5-3 |

### Chapter 6 6703/6704 Devices

| PCI/PXI-6703/6704 Analog Output Devices | . 6- | -1 |

|-----------------------------------------|------|----|

| PCI/PXI-6703/6704 Digital I/O           | 6-   | -1 |

### Chapter 7 PC-TIO-10 Timing I/O Device

| PC-TIO-10 Counter/Timer Operation           |     |

|---------------------------------------------|-----|

| Am9513-Based Device Counter/Timer Operation | 7-1 |

| Programmable Frequency Output Operation     | 7-5 |

| PC-TIO-10 Counter/Timers                    | 7-5 |

| PC-TIO-10 Digital I/O                       | 7-6 |

### Chapter 8 DIO-96 Digital I/O Devices

| D-96 Digital I/O8- | 1 |

|--------------------|---|

| DIO-96 Groups      | 2 |

# Chapter 9

# DIO-24 (6503), AT-MIO-16DE-10, and 6025E Devices

| DIO-24 ( | 6503), AT-MIO-16 | 5DE-10, and | 6025E Digital I/O | 9   | -1 |

|----------|------------------|-------------|-------------------|-----|----|

| DIO-24 ( | 6503), AT-MIO-16 | 5DE-10, and | 6025E Device Grou | ps9 | -2 |

### Chapter 10 DIO-32F and 6533 Digital I/O Devices

| DIO-32F and 6533 Digital I/O Devices10-1 |

|------------------------------------------|

|------------------------------------------|

### Chapter 11 AMUX-64T External Multiplexer Accessory

| AMUX-64T External Multiplexer Accessory | .11 | -1 |

|-----------------------------------------|-----|----|

| Scanning Order Using the AMUX-64T       |     | -2 |

### Chapter 12 SC-204*X* Accessories

| SC-2040 Track-and-Hold Accessory |  |

|----------------------------------|--|

| SC-2042-RTD Accessory            |  |

| SC-2043-SG Accessory             |  |

| 5C 2045 5G Accessory             |  |

### Chapter 13 SCC Series Modules

| SCC Shielded Carrier                        |  |

|---------------------------------------------|--|

| SCC Series Modules                          |  |

| SCC-A10 Voltage Attenuator Module           |  |

| SCC-AI Series Isolated Analog Input Modules |  |

| SCC-CI20 Current Input Module               |  |

| SCC-SG Series Strain-Gauge Modules          |  |

| SCC-TC01/02 Thermocouple Input Modules      |  |

| SCC-FT01 Feedthrough/Breadboard Module      |  |

| SCC-LP Lowpass Filter Modules               |  |

| SCC-DI01 Isolated Digital Input Module      |  |

|                                             |  |

| SCC-DO01 Isolated Digital Output Module | . 13-5 |

|-----------------------------------------|--------|

| SCC Configuration                       | . 13-5 |

### Chapter 14 SCXI Hardware

| SCXI Installation and Configuration                   |       |

|-------------------------------------------------------|-------|

| SCXI Operating Modes                                  |       |

| Multiplexed Mode for Analog Input Modules             | 14-2  |

| Multiplexed Mode for the SCXI-1200                    |       |

| Multiplexed Mode for Analog Output Modules            |       |

| Multiplexed Mode for Digital and Relay Modules        |       |

| Parallel Mode for Analog Input Modules                | 14-4  |

| Parallel (Standalone) Mode for the SCXI-1200          |       |

| Parallel Mode for Digital Modules                     |       |

| SCXI Modules and Compatible DAQ Devices               | 14-6  |

| SCXI Data Acquisition Device                          | 14-6  |

| SCXI-1200                                             | 14-6  |

| SCXI Analog Input Modules                             |       |

| SCXI-1100                                             | 14-7  |

| SCXI-1101                                             | -     |

| SCXI-1102, SCXI-1102B, and SCXI-1102C                 | 14-8  |

| SCXI-1104/C                                           | 14-9  |

| SCXI-1112                                             |       |

| SCXI-1120, SCXI-1120D, and SCXI-1121                  | 14-10 |

| SCXI-1125                                             | 14-11 |

| SCXI-1122                                             | 14-11 |

| SCXI-1126                                             | 14-12 |

| SCXI-1127                                             | 14-13 |

| SCXI-1140                                             |       |

| SCXI-1141, SCXI-1142, and SCXI-1143                   | 14-14 |

| SCXI Analog Output Module                             | 14-15 |

| SCXI-1124                                             | 14-15 |

| SCXI Digital Modules                                  |       |

| SCXI-1160 and SCXI-1161                               |       |

| SCXI-1162 and SCXI-1162HV                             | 14-17 |

| SCXI-1163 and SCXI-1163R                              |       |

| SCXI-1530, SCXI-1531                                  | 14-18 |

| SCXI-1540                                             |       |

| MIO and AI DAQ Devices (Except Parallel Port Devices) |       |

| Lab and 1200 Devices (Except Parallel Port Devices)   |       |

| DIO-24 and the DIO-96                                 | 14-22 |

| DIO-32F and 6533 Device                               | 14-23 |

### Chapter 15 VXI-DAQ Devices

| RTSI                                                           | 15-1 |

|----------------------------------------------------------------|------|

| VXI-DIO-128 Digital I/O Device                                 | 15-2 |

| VXI-AO-48XDC Analog Output Device                              |      |

| VXI-AO-48XDC Digital I/O                                       |      |

| VXI-MIO-64E-1 and VXI-MIO-64XE-10 Multifunction VXIbus Devices | 15-3 |

| VXI-DAQ Signal Conditioning                                    | 15-4 |

| VXI-SC-1102 Submodule                                          | 15-5 |

| VXI-SC-1102B and the VXI-SC-1102C Submodules                   | 15-5 |

| VXI-SC-1150 Submodule                                          | 15-5 |

### Chapter 16 PXI DAQ Devices

| RTSI                        | 16-1 |

|-----------------------------|------|

| PXI DAQ Signal Conditioning | 16-2 |

### Chapter 17 NI 5411 Devices

| NI 5411 Arbitrary Waveform and Pattern Generator Devices |      |

|----------------------------------------------------------|------|

| NI 5411 Device Characteristics                           |      |

| NI 5411 Device Waveform Generation                       |      |

| DDS Mode                                                 |      |

| NI 5411 Device Waveform Pattern Generation               |      |

| NI 5411 Device Pattern Generation Timing                 |      |

| NI 5411 Device Waveform Generation Triggering            |      |

| NI 5411 Device Feature Settings                          | 17-6 |

|                                                          |      |

### Chapter 18 NI 435*X* Devices

### Chapter 19 NI 40*XX* Devices

| NI 40XX Device Input                          |  |

|-----------------------------------------------|--|

| NI 40XX Data Acquisition                      |  |

| NI 40XX Data Acquisition Filtering and Timing |  |

### Chapter 20 DSA Devices

| PCI-445X and NI 455X Devices                           |  |

|--------------------------------------------------------|--|

| PCI-445X and NI 455X Analog Input Channels             |  |

| Data Acquisition                                       |  |

| Data Acquisition Timing                                |  |

| PCI-4451, PCI-4453, and NI 4551 Analog Output Channels |  |

| Waveform Generation                                    |  |

| PCI-445X and NI 455X Digital I/O                       |  |

| PCI-445X Digital I/O                                   |  |

| NI 455X Digital I/O                                    |  |

| PCI-445X and NI 455X Counter/Timer Operation           |  |

| PCI-445X Counter/Timers                                |  |

| NI 455X Counter/Timers                                 |  |

|                                                        |  |

### Chapter 21 671*X* Devices

| -1  |

|-----|

| -1  |

| -2  |

| -3  |

| l-3 |

| -3  |

| -3  |

|     |

### Chapter 22 652*X* Devices

### Appendix A Technical Support Resources

### Glossary

### Index

### Figures

| Figure 2-1.<br>Figure 2-2. | Lab and 1200 Device Interval Counter Block Diagram                                                                                                                                                                               |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-1.                | LPM Device Counter/Timer Signal Connections                                                                                                                                                                                      |

| Figure 4-1.<br>Figure 4-2. | DAQCard-700 Counter/Timer Signal Connections                                                                                                                                                                                     |

| Figure 7-1.<br>Figure 7-2. | Counter Block Diagram                                                                                                                                                                                                            |

| Figure 17-1.               | Examples of Waveform Generation                                                                                                                                                                                                  |

| S                          |                                                                                                                                                                                                                                  |

| Table 1.                   | MIO and AI Device Classificationxvi                                                                                                                                                                                              |

| Table 1-1.<br>Table 1-2.   | MIO and AI Multifunction I/O Device Analog<br>Input Characteristics1-1<br>AT-MIO-16DE-10 and 6025E Device Ports1-9                                                                                                               |

| Table 2-1.<br>Table 2-2.   | Lab and 1200 Devices and Corresponding FIFO Size                                                                                                                                                                                 |

| Table 3-1.                 | Maximum Recommended Data Acquisition Rates for the<br>LPM Devices                                                                                                                                                                |

| Table 7-1.                 | PC-TIO-10 Adjacent Counter Sequence                                                                                                                                                                                              |

| Table 8-1.                 | DIO-96 Port Labels, Numbers, and Modes                                                                                                                                                                                           |

| Table 9-1.                 | Digital I/O Device Port Numbers9-1                                                                                                                                                                                               |

|                            | Figure 2-2.<br>Figure 3-1.<br>Figure 4-1.<br>Figure 4-2.<br>Figure 7-1.<br>Figure 7-2.<br>Figure 17-1.<br><b>S</b><br>Table 1.<br>Table 1-1.<br>Table 1-2.<br>Table 2-1.<br>Table 2-2.<br>Table 3-1.<br>Table 7-1.<br>Table 8-1. |

#### Contents

| Table 11-1.<br>Table 11-2. | Analog Input Channel Range                                        |

|----------------------------|-------------------------------------------------------------------|

|                            |                                                                   |

| Table 11-3.                | AMUX-64T Scanning Order for Each MIO or AI Device                 |

|                            | Input Channel 11-3                                                |

| Table 13-1.                | SCC-AI Series Module Input/Output Range, Gain, and Bandwidth 13-3 |

| Table 15-1.                | RTSI Bus Line and VXIbus Trigger Mapping15-1                      |

| Table 16-1.                | RTSI Bus Line and PXI Bus Trigger Mapping16-1                     |

| Table 17-1.                | NI 5411 Device Characteristics                                    |

| Table 17-2.                | NI 5411 Operational Modes                                         |

| Table 18-1.                | Analog Input Ranges for the 435X Devices                          |

| Table 18-2.                | Ranges for 435X Device Data Acquisition                           |

| Table 18-3.                | Relationship between Filtering and Available Sample Rates         |

| Table 19-1.                | Relationship between Notch Filter Frequency and Power Line        |

|                            | Frequencies Filtered                                              |

| Table 19-2.                | Relationship between Notch Filter Frequency and                   |

|                            | Single-Channel Acquisition Rate                                   |

| Table 19-3.                | Relationship between Notch Filter Frequency and                   |

|                            | Single-Channel Acquisition Rate when AutoZero Is Enabled          |

| Table 20-1.                | PCI-445X and NI 455X Hardware Features                            |

| Table 22-1.                | Port Directions for the PCI/PXI-6527                              |

The *DAQ Hardware Overview Guide* is for users of the NI-DAQ software for PC compatibles version 6.7. NI-DAQ software is a powerful application programming interface (API) between your data acquisition (DAQ) application and your National Instruments DAQ devices.

# Conventions

|                        | The following conventions appear in this guide:                                                                             |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                        | This icon denotes a note, which alerts you to important information.                                                        |

| 1102/B/C modules       | Refers to the SCXI-1102, SCXI-1102B, and SCXI-1102C modules and the VXI-SC-1102, VXI-SC-1102B, and VXI-SC-1102C submodules. |

| 1200 and 1200AI device | Refers to the DAQCard-1200, DAQPad-1200, Lab-PC-1200, Lab-PC-1200AI, PCI-1200, and SCXI-1200.                               |

| 12-bit device          | These MIO and AI devices are listed in Table 1.                                                                             |

| 16-bit device          | These MIO and AI devices are listed in Table 1.                                                                             |

| 1394                   | Refers to a high-speed external bus that implements the IEEE 1394 serial bus protocol.                                      |

| 435X device            | Refers to the NI 4350 for ISA, PCMCIA, USB, and NI 4351 for PCI and PXI.                                                    |

| 445X device            | Refers to the PCI-4451, PCI-4452, PCI-4453, and PCI-4454.                                                                   |

| 455X device            | Refers to the NI 4551 and NI 4552.                                                                                          |

| 516 device             | Refers to the DAQCard-516 and PC-516.                                                                                       |

| 6025E device           | Refers to the PCI-6025E and PXI-6025E.                                                                                      |

| 6052E device           | Refers to the PCI-6052E, PXI-6052E, and DAQPad-6052E for 1394.                                                              |

| 611X device            | Refers to the PCI-6110E and PCI-6111E.                                                                                      |

| 6602 device            | Refers to the PCI-6602 and PXI-6602.                                                                                        |

| 6703/6704 device       | Refers to the PCI-6703/6704 and PXI-6703/6704.                                                                              |

#### About This Guide

| 671X device                       | Refers to the DAQCard-6715, PCI-6711, PXI-6711, PCI-6713, and PXI-6713.                                                                                                                            |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AI device                         | These analog input devices are listed in Table 1.                                                                                                                                                  |

| bold                              | Bold text denotes items that you must select or click on in the software,<br>such as menu items and dialog box options. Bold text also denotes<br>parameter names.                                 |

| DAQCard-500/700                   | Refers to the DAQCard-500 and DAQCard-700.                                                                                                                                                         |

| DIO 6533                          | Refers to the AT-DIO-32HS, PCI-DIO-32HS, DAQCard-6533, and PXI-6533.                                                                                                                               |

| DIO-24                            | Refers to the PC-DIO-24, PC-DIO-24PnP, DAQCard-DIO-24 and 6503 devices.                                                                                                                            |

| DIO-32F                           | Refers to the AT-DIO-32F.                                                                                                                                                                          |

| DIO-96                            | Refers to the PC-DIO-96, PC-DIO-96PnP, PCI-DIO-96, DAQPad-6507, DAQPad-6508, and PXI-6508.                                                                                                         |

| DIO device                        | Refers to any DIO-24, DIO-32, DIO-6533, or DIO-96.                                                                                                                                                 |

| DSA device                        | Refers to the PCI-4451, PCI-4452, PCI-4453, PCI-4454, NI 4551, and NI 4552.                                                                                                                        |

| E Series device                   | These are MIO and AI devices. Refer to Table 1 for a complete list of these devices.                                                                                                               |

| italic                            | Italic text denotes variables, emphasis, a cross reference, or an introduction<br>to a key concept. This font also denotes text that is a placeholder for a word<br>or value that you must supply. |

| Lab and 1200 device               | Refers to the DAQCard-1200, DAQPad-1200, Lab-PC+, Lab-PC-1200, Lab-PC-1200AI, PCI-1200, and SCXI-1200.                                                                                             |

| Lab and 1200 analog output device | Refers to the DAQCard-1200, DAQPad-1200, Lab-PC+, Lab-PC-1200, PCI-1200, and SCXI-1200.                                                                                                            |

| LPM device                        | Refers to the PC-LPM-16 and PC-LPM-16PnP.                                                                                                                                                          |

| MIO device                        | Refers to multifunction I/O devices. See Table 1 for a list of these devices.                                                                                                                      |

| MIO-16XE-50 device                | Refers to the AT-MIO-16XE-50, DAQPad-MIO-16XE-50, and NEC-MIO-16XE-50, and PCI-MIO-16XE-50.                                                                                                        |

| MIO-64                    | Refers to the AT-MIO-64E-4, PCI-6031E, PCI-6071E, VXI-MIO-64E-1, and VXI-MIO-64XE-10.                                                                                                                                                                                                                                                                               |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| monospace                 | Text in this font denotes text or characters that you should enter from the keyboard, sections of code, programming examples, and syntax examples. This font is also used for the proper names of disk drives, paths, directories, programs, subprograms, subroutines, device names, functions, operations, variables, filenames and extensions, and code excerpts. |

| NI 40XX device            | Refers to the NI 4050 for PCMCIA, and NI 4060 for PCI and PXI.                                                                                                                                                                                                                                                                                                      |

| NI 5411 device            | Refers to the NI 5411 for ISA and PCI.                                                                                                                                                                                                                                                                                                                              |

| NI-DAQ                    | Refers to the NI-DAQ software for PC compatibles, unless otherwise noted.                                                                                                                                                                                                                                                                                           |

| NI-TIO based device       | Refers to the NI 4551, PCI-6608, PCI-6602, and PXI-6602.                                                                                                                                                                                                                                                                                                            |

| PC                        | Refers to the IBM PC/XT, IBM PC AT, and compatible computers.                                                                                                                                                                                                                                                                                                       |

| PCI Series                | Refers to the National Instruments products that use the high-performance expansion bus architecture originally developed by Intel to replace ISA and EISA.                                                                                                                                                                                                         |

| Remote SCXI               | Refers to an SCXI configuration where either an SCXI-2000 chassis or an SCXI-2400 remote communications module is connected to the PC serial port.                                                                                                                                                                                                                  |

| SCXI-1102/B/C             | SCXI-1102/B/C refers to the SCXI-1102, SCXI-1102B, and SCXI-1102C devices.                                                                                                                                                                                                                                                                                          |

| SCXI-1104/C               | SCXI-1104/C refers to the SCXI-1104 and SCXI-1104/C.                                                                                                                                                                                                                                                                                                                |

| SCXI-1120/D               | SCXI-1120/D refers to the SCXI-1120 and SCXI-1120D.                                                                                                                                                                                                                                                                                                                 |

| SCXI analog input module  | Refers to the SCXI-1100, SCXI-1101, SCXI-1102, SCXI-1104, SCXI-1112, SCXI-1120, SCXI-1120D, SCXI-1121, SCXI-1122, SCXI-1125, SCXI-1127, SCXI-1140, SCXI-1141, SCXI-1142, and SCXI-1143.                                                                                                                                                                             |

| SCXI chassis              | Refers to the SCXI-1000, SCXI-1000DC, SCXI-1001, and SCXI-2000.                                                                                                                                                                                                                                                                                                     |

| SCXI communication module | Refers to the SCXI-2400.                                                                                                                                                                                                                                                                                                                                            |

| SCXI DAQ module           | Refers to the SCXI-1200.                                                                                                                                                                                                                                                                                                                                            |

| SCXI digital module          | Refers to the SCXI-1160, SCXI-1161, SCXI-1162, SCXI-1162HV, SCXI-1163, and SCXI-1163R. |

|------------------------------|----------------------------------------------------------------------------------------|

| Simultaneous sampling device | Refers to the PCI-6110E, PCI-6111E, PCI-4451, PCI-4452, NI 4551, and NI 4552.          |

| VXI-MIO device               | Refers to the VXI-MIO-64E-1 and VXI-MIO-64XE-10.                                       |

| VXI-SC-1102/B/C              | Refers to the VXI-SC-1102, VXI-SC-1102B, and VXI-SC-1102C.                             |

### **MIO and AI Device Terminology**

This guide uses generic terms to describe groups of devices whenever possible. The generic terms for the MIO and AI devices are based on the number of bits, the platform, and the functionality. These devices are also collectively known as E Series devices. Table 1 lists each MIO and AI device and the possible classifications for each.

| Device             | Number<br>of SE<br>Channels | Bit    | Туре             | Functionality |

|--------------------|-----------------------------|--------|------------------|---------------|

| AT-AI-16XE-10      | 16                          | 16-bit | AT               | AI            |

| AT-MIO-16DE-10     | 16                          | 12-bit | AT               | MIO           |

| AT-MIO-16E-1       | 16                          | 12-bit | AT               | MIO           |

| AT-MIO-16E-2       | 16                          | 12-bit | AT               | MIO           |

| AT-MIO-16E-10      | 16                          | 12-bit | AT               | MIO           |

| AT-MIO-16XE-10     | 16                          | 16-bit | AT               | MIO           |

| AT-MIO-16XE-50     | 16                          | 16-bit | AT               | MIO           |

| AT-MIO-64E-3       | 64                          | 12-bit | AT               | MIO           |

| DAQCard-AI-16E-4   | 16                          | 12-bit | PCMCIA           | AI            |

| DAQCard-AI-16XE-50 | 16                          | 16-bit | PCMCIA           | AI            |

| DAQCard-6023E      | 16                          | 12-bit | PCMCIA           | AI            |

| DAQCard-6024E      | 16                          | 12-bit | PCMCIA           | MIO           |

| DAQCard-6062E      | 16                          | 12-bit | PCMCIA           | MIO           |

| DAQPad-MIO-16XE-50 | 16                          | 16-bit | Parallel<br>Port | MIO           |

| DAQPad-6020E       | 16                          | 12-bit | USB              | MIO           |

Table 1. MIO and AI Device Classification

| Number                  |                   |                         |      |               |  |  |

|-------------------------|-------------------|-------------------------|------|---------------|--|--|

| Device                  | of SE<br>Channels | Bit                     | Туре | Functionality |  |  |

| DAQPad-6052E            | 16                | 16-bit                  | 1394 | MIO           |  |  |

| DAQPad-6070E            | 16                | 12-bit                  | 1394 | MIO           |  |  |

| NEC-AI-16E-4            | 16                | 12-bit                  | NEC  | AI            |  |  |

| NEC-AI-16XE-50          | 16                | 16-bit                  | NEC  | AI            |  |  |

| NEC-MIO-16E-4           | 16                | 12-bit                  | NEC  | MIO           |  |  |

| NEC-MIO-16XE-50         | 16                | 16-bit                  | NEC  | MIO           |  |  |

| PCI-6023E               | 16                | 12-bit                  | PCI  | AI            |  |  |

| PCI-6024E               | 16                | 12-bit                  | PCI  | MIO           |  |  |

| PCI-6025E               | 16                | 12-bit                  | PCI  | MIO           |  |  |

| PCI-6031E (MIO-64XE-10) | 64                | 16-bit                  | PCI  | MIO           |  |  |

| PCI-6032E (AI-16XE-10)  | 16                | 16-bit                  | PCI  | AI            |  |  |

| PCI-6033E (AI-64XE-10)  | 64                | 16-bit                  | PCI  | AI            |  |  |

| PCI-6052E               | 16                | 16-bit                  | PCI  | MIO           |  |  |

| PCI-6071E (MIO-64E-1)   | 64                | 12-bit                  | PCI  | MIO           |  |  |

| PCI-6110E               | 4 DIFF<br>only    | 12-bit AI,<br>16-bit AO | PCI  | MIO           |  |  |

| PCI-6111E               | 2 DIFF<br>only    | 12-bit AI,<br>16-bit AO | PCI  | MIO           |  |  |

| PCI-MIO-16E-1           | 16                | 12-bit                  | PCI  | MIO           |  |  |

| PCI-MIO-16E-4           | 16                | 12-bit                  | PCI  | MIO           |  |  |

| PCI-MIO-16XE-10         | 16                | 16-bit                  | PCI  | MIO           |  |  |

| PCI-6034E               | 16                | 16-bit                  | PCI  | AI            |  |  |

| PXI-6034E               | 16                | 16-bit                  | PXI  | AI            |  |  |

| PCI-6035E               | 16                | 16-bit AI<br>12-bit AO  | PCI  | MIO           |  |  |

| PXI-6035E               | 16                | 16-bit AI<br>12-bit AO  | PXI  | MIO           |  |  |

| PCI-MIO-16XE-50         | 16                | 16-bit                  | PCI  | MIO           |  |  |

| PXI-6011E               | 16                | 16-bit                  | PXI  | MIO           |  |  |

Table 1. MIO and AI Device Classification (Continued)

| Device          | Number<br>of SE<br>Channels | Bit    | Туре | Functionality |

|-----------------|-----------------------------|--------|------|---------------|

|                 | Channels                    | Dit    | турс | Functionanty  |

| PXI-6023E       | 16                          | 12-bit | PXI  | AI            |

| PXI-6024E       | 16                          | 12-bit | PXI  | MIO           |

| PXI-6025E       | 16                          | 12-bit | PXI  | MIO           |

| PXI-6030E       | 16                          | 16-bit | PXI  | MIO           |

| PXI-6040E       | 16                          | 12-bit | PXI  | MIO           |

| PXI-6052E       | 16                          | 16-bit | PXI  | MIO           |

| PXI-6070E       | 16                          | 12-bit | PXI  | MIO           |

| VXI-MIO-64E-1   | 64                          | 12-bit | VXI  | MIO           |

| VXI-MIO-64XE-10 | 64                          | 16-bit | VXI  | MIO           |

Table 1. MIO and AI Device Classification (Continued)

# **Related Documentation**

For detailed hardware information, refer to the user manual included with each device. For detailed software information, refer to your NI-DAQ for PC compatibles documentation.

# **MIO and AI Devices**

This chapter contains overview information on the MIO and AI devices. These devices are listed in Table 1-1.

# **MIO and AI Multifunction I/O Devices**

The National Instruments MIO and AI devices are collectively known as E Series devices. Timing and control on these devices is performed by the National Instruments Data Acquisition System Timing Controller (DAQ-STC) chip.

### **MIO and AI Device Analog Input**

Table 1-1 summarizes the key analog input characteristics for the MIO and AI multifunction I/O devices.

| Device                                           | Number<br>of<br>Channels | ADC<br>Resolution<br>(Bits) | Gains                               | Range (V)   | Input<br>FIFO<br>(Words) | Hardware<br>Analog<br>Trigger |

|--------------------------------------------------|--------------------------|-----------------------------|-------------------------------------|-------------|--------------------------|-------------------------------|

| AT-MIO-16DE-10,<br>AT-MIO-16E-10<br>DAQPad-6020E | 16                       | 12                          | 0.5, 1, 2, 5, 10,<br>20, 50, 100    | ±5, 0 to 10 | 512                      | no                            |

| AT-MIO-16E-1                                     | 16                       | 12                          | 0.5, 1, 2, 5, 10,<br>20, 50, 100    | ±5, 0 to 10 | 8,192                    | yes                           |

| AT-MIO-16E-2,<br>NEC-AI-16E-4,<br>NEC-MIO-16E-4  | 16                       | 12                          | 0.5, 1, 2, 5, 10,<br>20, 50, 100    | ±5, 0 to 10 | 2,048                    | yes                           |

| 6023E, 6024E,<br>6025E devices                   | 16                       | 12                          | 0.5, 1, 10, 100                     | ±5          | 512                      | no                            |

| 6034E, 6035E devices                             | 16                       | 16                          | 0.5, 1, 10, 100                     | ±5          | 512                      | no                            |

| DAQPad-6070E                                     | 16                       | 12                          | 0.5, 1, 2.5, 5, 10,<br>20, 50, 100, | ±5, 0 to 10 | 2,048                    | yes                           |

Table 1-1. MIO and AI Multifunction I/O Device Analog Input Characteristics

|                                                                                                  | Number         | ADC                  |                                     |              | Input           | Hardware          |

|--------------------------------------------------------------------------------------------------|----------------|----------------------|-------------------------------------|--------------|-----------------|-------------------|

| Device                                                                                           | of<br>Channels | Resolution<br>(Bits) | Gains                               | Range (V)    | FIFO<br>(Words) | Analog<br>Trigger |

| PCI-MIO-16E-4,<br>PCI-MIO-16E-1,<br>PXI-6040E,<br>PXI-6070E                                      | 16             | 12                   | 0.5, 1, 2.5, 5, 10,<br>20, 50, 100, | ±5, 0 to 10  | 512             | yes               |

| DAQCard-AI-16E-4                                                                                 | 16             | 12                   | 0.5, 1, 2, 5, 10,<br>20, 50, 100    | ±5, 0 to 10  | 1,024           | yes               |

| AT-MIO-16XE-10,<br>AT-AI-16XE-10                                                                 | 16             | 16                   | 1, 2, 5, 10, 20,<br>50, 100         | ±10, 0 to 10 | 2,048           | yes               |

| AT-MIO-16XE-50,<br>DAQPad-MIO-16XE-50,<br>NEC-AI-16XE-50,<br>NEC-MIO-16XE-50,<br>PCI-MIO-16XE-50 | 16             | 16                   | 1, 2, 10, 100                       | ±10, 0 to 10 | 512             | no                |

| DAQCard-AI-16XE-50                                                                               | 16             | 16                   | 1, 2, 10, 100                       | ±10, 0 to 10 | 1,024           | no                |

| AT-MIO-64E-3                                                                                     | 64             | 12                   | 0.5, 1, 2, 5, 10,<br>20, 50, 100    | ±5, 0 to 10  | 2,048           | yes               |

| PCI-MIO-16XE-10,<br>PCI-6032E<br>(AI-16XE-10)<br>PXI-6030E                                       | 16             | 16                   | 1, 2, 5, 10, 20,<br>50, 100         | ±10, 0 to 10 | 512             | yes               |

| 6052E devices                                                                                    | 16             | 16                   | 0.5, 1, 2.5, 5, 10,<br>20, 50, 100  | ±5, 0 to 10  | 512             | yes               |

| VXI-MIO-64E-1                                                                                    | 64             | 12                   | 0.5, 1, 2, 5, 10,<br>20, 50, 100    | ±5, 0 to 10  | 8,192           | yes               |

| PCI-6110E                                                                                        | 4              | 12                   | 0.2, 0.5, 1, 2, 5,<br>10, 20, 50    | ±10          | 512             | yes               |

| PCI-6111E                                                                                        | 2              | 12                   | 0.2, 0.5, 1, 2, 5,<br>10, 20, 50    | ±10          | 512             | yes               |

| PCI-6031E<br>(MIO-64XE-10),<br>PCI-6033E (AI-64XE-10)<br>VXI-MIO-64XE-10                         | 64             | 16                   | 1, 2, 5, 10, 20,<br>50,100          | ±10, 0 to 10 | 512             | yes               |

| PXI-6071E<br>(MIO-64E-1)                                                                         | 64             | 12                   | 0.5, 1, 2, 5, 10,<br>20, 50, 100    | ±5, 0 to 10  | 512             | yes               |

Table 1-1.

MIO and AI Multifunction I/O Device Analog Input Characteristics (Continued)

| Device        | Number<br>of<br>Channels | ADC<br>Resolution<br>(Bits) | Gains                            | Range (V) | Input<br>FIFO<br>(Words) | Hardware<br>Analog<br>Trigger |

|---------------|--------------------------|-----------------------------|----------------------------------|-----------|--------------------------|-------------------------------|

| DAQCard-6023E | 16                       | 12                          | 0.5, 1, 10, 100                  | ±5        | 2048                     | no                            |

| DAQCard-6024E | 16                       | 12                          | 0.5, 1, 10, 100                  | ±5        | 2048                     | no                            |

| DAQCard-6062E | 16                       | 12                          | 0.5, 1, 2, 5, 10,<br>20, 50, 100 | ±5        | 8192                     | yes                           |

Table 1-1. MIO and AI Multifunction I/O Device Analog Input Characteristics (Continued)

Note Terms such as ADC resolution and analog trigger are defined in the Glossary.

### **E Series Data Acquisition**

The E Series devices can perform single-channel data acquisitions and multiple-channel scanned data acquisitions. For single-channel data acquisition, select a single analog input channel and gain setting. The device performs a single A/D conversion on that channel every sample interval.

For multiple-channel scanned data acquisition, the device scans a set of analog input channels, each with its own gain setting. In this method, a scan sequence indicates which analog channels to scan and the gain settings for each channel. The length of this scan sequence can be 1 to 512 channel/gain pairs. For the PCI-6110E and the PCI-6111E each channel can appear only once in the scan sequence.

During scanning, the analog input circuitry performs an A/D conversion on the next entry in the scan sequence. The device performs an A/D conversion once every sample interval. For maximum performance, this operation is pipelined so that the device switches to the next channel while the current A/D conversion is performed. The device waits for a specified scan interval before scanning the channels again. The channels are scanned repeatedly at the beginning of each scan interval until the required number of samples has been acquired. For example, you can scan a sequence of four channels once every 10 s. The device could sample the channels at the beginning of the 10 s interval, within 20  $\mu$ s, with a 5  $\mu$ s sample interval between channels. If you set the scan interval to 0, the scan sequence starts over again immediately at the end of each scan sequence without waiting for a scan interval. The 0 scan interval setting causes the device to scan the channels repeatedly as fast as possible.

**Note** The 611X devices sample all channels simultaneously. The scan interval controls the sampling rate, therefore the scan interval of zero is not allowed.

M

You can combine both single-channel and multiple-channel acquisition with any of the following additional modes:

- Posttrigger mode

- Pretrigger mode

- Double-buffered mode

- AMUX-64T mode

- SCXI mode

Note The 611X devices do not support the AMUX-64T or SCXI modes.

Posttrigger mode collects a specified number of samples after the device receives a trigger. Refer to the *stop trigger* discussion in the appropriate data acquisition timing section for your device later in this chapter for details. After the user-specified buffer is full, the data acquisition stops.

Pretrigger mode collects data both before and after the device receives a trigger, either through software or by applying a hardware signal. The device collects samples and fills the user-specified buffer without stopping until the device receives the *stop trigger* signal. Refer to the stop trigger discussion in the appropriate data acquisition timing section for your device later in this chapter for details. The device then collects a specified number of samples and stops the acquisition. The buffer is treated as a circular buffer—when the entire buffer has been written to, data is stored at the beginning again, overwriting the old data. When data acquisition stops, the buffer has samples from before and after the stop trigger occurred. The number of samples saved depends on the length of the user-specified buffer and on the number of samples specified to be acquired after receipt of the trigger.

Double-buffered mode, like pretrigger mode, also fills the user-specified buffer continuously. You can call DAQ\_DB\_Transfer to transfer old data into a second buffer before it is overwritten by new data. DAQ\_DB\_Transfer transfers data out of one half of the buffer while the other half is filled with new data.

In the AMUX-64T mode, you use one, two, or four external AMUX-64T devices to extend the number of analog input channels available. You connect the external signals to the AMUX-64T device pins, instead of directly to the DAQ device pins.

You can use SCXI modules as a data acquisition front end for the device to condition the input signals and multiplex the channels. You can use all the modes just described in conjunction with SCXI. The *SCXI Modules and Compatible DAQ Devices* section in Chapter 14, *SCXI Hardware*, describes how to use the SCXI functions to set up the SCXI modules for a data acquisition to be performed by a DAQ device.

**Note** The DAQPad-MIO-16XE-50 uses half-FIFO mode by default when doing interrupt data transfer operations for analog input with rates faster than 256 samples per second. The PCI E Series and DAQCard E Series devices use half-FIFO when performing interrupt data transfers for analog input with rates faster than 1000 samples per second. You can override the default setting and select between interrupt on every sample and interrupt on half-FIFO. When using external conversions, you should select the mode appropriate for the acquisition rate. To set the interrupt generation mode, see the Set\_DAQ\_Device\_Info function in the *NI-DAQ Function Reference Online Help* or the Set\_DAQ\_Device\_Info.vi in the *LabVIEW DAQ Online Reference*.

### E Series Data Acquisition Timing

$\mathbb{N}$

The following DAQ-STC counters are used for data acquisition timing and control:

- The *scan counter* is used to control the number of scans you will acquire. If you want to perform pretriggered acquisition, this counter will ensure that you acquire selected number of scans before the stop trigger is recognized.

- The *scan timer* is a counter that you can use for *start scan* timing.

- The *sample-interval timer* is a counter that you can use for *conversion* timing.

The DAQPad-6020E uses half-FIFO mode when doing interrupt data transfer operations for analog input rates of > 256 samples per second.

Data acquisition timing involves the following timing signals:

- A *start trigger* is a signal that initiates a data acquisition sequence. You can supply this signal externally through a selected I/O connector pin, through a RTSI bus trigger line, or by software.

- A *start scan* signal initiates individual scans. This signal can be supplied from the onboard programmable scan timer, externally through a selected I/O connector pin, through a RTSI bus trigger line, or by software.

- A *conversion* signal initiates individual analog-to-digital (A/D) conversions. This signal can be supplied from the onboard programmable sample timer, externally through a selected I/O connector pin, through a RTSI bus trigger line, or by software.

- A *stop trigger* is a signal used for pretriggered data acquisition to notify your device to stop acquiring data after a specified number of scans. Data acquisition operation is continuously performed until the device receives this signal. This signal can be supplied externally through a selected I/O connector pin, through a RTSI bus trigger line, or by software.

- A *gate* is a signal used for gating the data acquisition. When you enable gating, the data acquisition will proceed only on selected level of the gate signal. This signal can be supplied externally through a selected I/O connector pin, through a RTSI bus trigger line.

- A *scan timer timebase* is a signal used by the scan timer for scan interval timing. This signal is used only when the scan timer is used. This signal can be supplied from one of the onboard timebase sources, externally through a selected I/O connector pin, or through a RTSI bus trigger line.

- A *sample-interval timer timebase* is a signal used by the sample interval timer for conversion timing. This signal is used only when the sample interval timer is used. This signal can be supplied from one of the onboard timebase sources, externally through a selected I/O connector pin, or through a RTSI bus trigger line.

See your DAQ device user manual for more information regarding these signals.

DAQ devices with the DAQ-STC use two counters, the scan interval counter and the sample interval counter. The E Series devices support both internal and external timebases. The internal timebases available on the DAQ-STC are 20 MHz (50 ns) and 100 kHz (10  $\mu$ s). The scan interval counter is a 24-bit counter, and the sample interval counter is a 16-bit counter.

While the scan interval counter has the freedom to work with both internal and external timebases, the sample interval counter can use either the 20 MHz timebase or the timebase used by the scan interval counter.

When you specify a timebase value different from the internal timebases the DAQ-STC uses, NI-DAQ tries to convert the timebase and interval values you specified into those that the DAQ-STC can use. If NI-DAQ cannot make the translation without a loss of resolution, it returns **rateNotSupportedError**. This typically occurs if you specified a timebase of 5 (100 Hz) and a sample interval of 100, for example, for a resulting sample interval of 1 s. This generates an error because the sample interval counter rolls over before 1 s.

**Note** The 611X devices use the scan interval counter to control the acquisition rate. The sample interval counter does not affect conversion timing since all channels are sampled simultaneously. The pipelined ADC used on 611X devices requires four conversions before the first sample becomes available; therefore, if you are using external conversions, you should allow for this behavior.

### **E Series Data Acquisition Rates**

Refer to the appropriate user manual for single-channel and multiple-channel DAQ rates and settling accuracy.

If you are using SCXI with your DAQ device, refer to the *SCXI Data Acquisition Rates* section in Chapter 3, *Software Overview*, of the *NI-DAQ User Manual for PC Compatibles*, for the effect of SCXI module settling time on your data acquisition device rates.

### **MIO Device Analog Output**

The MIO devices contain two analog output channels numbered 0 and 1. Each analog output channel contains either a 12-bit DAC or a 16-bit DAC, depending on the AO resolution of your device. You can configure each analog output channel for unipolar or bipolar voltage output except on the MIO-16XE-50 and the 611*X* devices, which are always in bipolar mode. An onboard voltage reference of +10 V is available for the analog output channels except on the MIO-16XE-50 and the MIO-16XE-10, MIO-16XE-50 and the 611*X* devices. See the AO\_Configure function in the *NI-DAQ Function Reference Online Help* or the AO\_Configure.vi in the *LabVIEW DAQ Online Reference* for more information about configuring the DACs.

**Note** The 611X devices require an even number of samples in the waveform buffer due to a 32-bit wide output FIFO necessary for high-speed data transfers.

### **MIO Device Waveform Generation**

The Waveform Generation functions can write values to either one or both analog output channels continuously using an onboard or external clock to update the DACs at regular intervals. The values are contained in a buffer that you allocate and fill. The resultant voltages produced at the analog

$\mathbb{N}$

output channels depend on the value of the numbers in the buffer, the level of the reference voltage, and the polarity setting.

**Note** (E Series devices on VXI, ISA, PCI, PXI and 1394 buses only) NI-DAQ can use either DMA or interrupt service routines to generate waveforms on the analog output channels. By default, NI-DAQ uses DMA because DMA is simply more efficient. If you prefer to reserve the DMA channels for the Data Acquisition functions or for other devices in the system, call Set\_DAQ\_Device\_Info, described in the *NI-DAQ Function Reference Online Help*, or the Set\_DAQ\_Device\_Info.vi in the *LabVIEW DAQ Online Reference* to force NI-DAQ not to use DMA for waveform generation.

### E Series Waveform Generation Using Onboard Memory

All E Series devices with analog output FIFOs support FIFO mode waveform generation. In this mode, waveform data is transferred to the onboard DAC FIFO memory only once. These values are then cycled through to generate the waveform continuously or for a finite number of iterations. No interrupt service or DMA operation is required to transfer more data to the device during waveform generation.

The following conditions must be satisfied to use FIFO mode waveform generation:

- One cycle worth of waveform data can be held entirely on the device DAC FIFO memory.

- Double-buffered waveform generation mode is disabled.

- The number of cycles to generate can be infinite, denoted by the value 0, or between 1 and 16,777,216 inclusive.

There are two variations possible in FIFO mode waveform generation:

- Continuous cyclic waveform generation—An onboard counter or an external signal provides the update pulses. Once started, the waveform generation continues until you call the clear function to stop the waveform.

- Programmed cyclic waveform generation—An onboard counter or an external signal provides the update pulses. A separate onboard counter terminates the waveform after a finite number of cycles has been generated.

Refer to your DAQ device manual to determine the size of the analog output FIFO and for more information on waveform generation.

### E Series Digital I/O

M

The E Series devices contain one 8-bit digital I/O port supplied by the DAQ-STC chip. This port is referred to as port 0 by the Digital I/O functions.

You can configure the entire digital port as either an input or an output port, or you can configure individual lines for either input or output. The port has *read-back capability*. This port operates in nonlatched mode only.

**Note** Connecting one or more AMUX-64T devices or a non-remote SCXI chassis to an E Series device renders various lines of the digital I/O port unavailable:

- One AMUX-64T device—Lines 0 and 1 are unavailable.

- Two AMUX-64T devices—Lines 0, 1, and 2 are unavailable.

- Four AMUX-64T devices—Lines 0, 1, 2, and 3 are unavailable.

- SCXI—Lines 0, 1, 2, and 4 are unavailable.

The remaining lines of the digital I/O port are available for input or output. You should use DIG\_Line\_Config to configure these remaining lines.

The AT-MIO-16DE-10 and the 6025E devices have one 8-bit line-configurable port named port 0 that does not support handshaking or asynchronous operations. The DAQ-STC chip supplies this port. The AT-MIO-16DE-10 and the 6025E devices also have three 8-bit ports named ports 2, 3, and 4 that do support handshaking and asynchronous operations and are directionally configurable only on a per-port basis. An 8255 chip supplies these three ports. The three 8255 ports are numbered 2, 3, and 4 for compatibility with an older product. Table 1-2 summarizes the four ports available on the AT-MIO-16DE-10 and the 6025E devices.

| Port | Size  | Configuration     | Туре                      | Supplied by  |

|------|-------|-------------------|---------------------------|--------------|

| 0    | 8-bit | Line configurable | Immediate                 | DAQ-STC chip |

| 2    | 8-bit | Handshaking       | Asynchronous or immediate | 8255 chip    |

| 3    | 8-bit | Handshaking       | Asynchronous or immediate | 8255 chip    |

| 4    | 8-bit | _                 | Immediate                 | 8255 chip    |

For a description of the AT-MIO-16DE-10 and the 6025E device digital I/O, see Chapter 9, *DIO-24 (6503), AT-MIO-16DE-10, and 6025E Devices*.

### **E Series Counter/Timer Operation**

The E Series devices use the National Instruments DAQ-STC counter/timer chip. The DAQ-STC has two 24-bit counter/timers that are always available for general-purpose counter/timer applications. Refer to the GPCTR functions in the *NI-DAQ Function Reference Online Help* for more information.

### **E Series Programmable Frequency Output Operation**

The E Series devices have one I/O connector pin (FREQ\_OUT) capable of outputting a programmable frequency signal. This signal is a divided-down version of the selected timebase. Available timebases for this operation are 10 MHz and 100 kHz, and you can divide them by numbers 1 through 16.

### **E Series PFI Pins**

You can route internal device signals to and from the I/O connector programmatically by using the PFI pins on the E Series devices. Refer to your E Series device user manual for a complete discussion of PFI pins. See the Select\_Signal function description in the *NI-DAQ Function Reference Online Help* for programming information on routing.

# Lab and 1200 Devices

This chapter contains overview information on the DAQCard-1200, DAQPad-1200, Lab-PC+, Lab-PC-1200, Lab-PC-1200AI, PCI-1200, and SCXI-1200 devices.

# Lab and 1200 Devices Analog Input

The Lab and 1200 devices contain eight single-ended analog input channels numbered 0 through 7. The analog input channels are multiplexed into a single programmable gain stage and 12-bit ADC. The devices have gains of 1, 2, 5, 10, 20, 50, and 100.

You can configure the input channels to be differential or nonreferenced single ended. In differential mode, four channels are available, namely, 0, 2, 4, and 6. All Lab and 1200 devices except the Lab-PC+ support software configuration of the input mode; on the Lab-PC+, configure the mode via jumper W4.

You can hardware jumper-configure analog input on the Lab-PC+ and software configure analog input on all other Lab and 1200 devices for two different input ranges:

- 0 to +10 V (unipolar)

- -5 to +5 V (bipolar)

You can initiate A/D conversions through software or by applying active low pulses to the EXTCONV\* input on the device I/O connector. Each of the devices has a FIFO on the device in which to store the results of A/D conversions temporarily. Table 2-1 shows the FIFO sizes.

| Table 2-1. | Lab and 1200 Devices and Corresponding FIFO Size |

|------------|--------------------------------------------------|

|------------|--------------------------------------------------|

| Device                                                                           | FIFO Size (in words) |

|----------------------------------------------------------------------------------|----------------------|

| Lab-PC+                                                                          | 512                  |

| DAQCard-1200, DAQPad-1200,<br>Lab-PC-1200, Lab-PC-1200AI, PCI-1200,<br>SCXI-1200 | 2,048                |

### Lab and 1200 Devices Data Acquisition

The Lab and 1200 devices can perform single-channel data acquisition and multiple-channel scanned data acquisition. For single-channel data acquisition, you select a single analog input channel and gain setting. The device performs a single A/D conversion on that channel every sample interval.

For multiple-channel scanned data acquisition, the devices scan a sequence of analog input channels. A single gain setting is used for all channels scanned. A *sample interval* indicates the time to elapse between A/D conversions on each channel in the sequence. You need only to select a single starting channel to select the sequence of channels to scan. The device then scans the channels in consecutive order until channel 0 is reached, and then the scan begins anew with the starting channel. For example, if the starting channel is channel 3, the scan sequence is as follows:

channel 3, channel 2, channel 1, channel 0, channel 3, and so on

The Lab and 1200 devices support interval scanning. A scan interval is the time that elapses between two channel-scanning cycles.

You can combine both the single-channel and multiple-channel acquisitions with any of the following additional modes:

- Posttrigger mode

- Pretrigger mode

- Double-buffered mode

- SCXI mode (except the DAQPad-1200)

Posttrigger mode collects a specified number of samples after the device receives a trigger. You can initiate posttrigger acquisition through software or when a pulse edge is applied to the EXTTRIG input. After the user-specified buffer has been filled, the data acquisition stops.

Pretrigger mode collects data both before and after the device receives a trigger. You can initiate data acquisition through software. The device collects samples and fills the user-specified buffer without stopping or counting samples until the device receives a pulse at the EXTTRIG input. The device then collects a specified number of samples and stops the acquisition. The buffer is treated as a circular buffer—when the entire buffer has been written to, data is stored at the beginning again, overwriting the old data. When data acquisition stops, the buffer has samples from before and after the stop trigger occurred. The number of samples saved

depends on the length of the user-specified buffer and on the number of samples specified to be acquired after receipt of the trigger.

Because there is only one EXTTRIG input on the device I/O connector, a single acquisition cannot employ both of these trigger modes.

Double-buffered mode, like pretrigger mode, also fills the user-specified buffer continuously. Unlike pretrigger mode, however, double-buffered mode transfers old data into a second buffer before overwriting the old data with new data. Data is transferred out of one half of the buffer while the other half is being filled with new data. You can use double-buffered mode in conjunction with either pretrigger or posttrigger modes.

You can use SCXI modules as a data acquisition front end for all Lab and 1200 devices except the DAQPad-1200 to signal condition the input signals and multiplex the channels. You can use all the modes just described in conjunction with SCXI for single-channel acquisitions; however, onboard multiple-channel acquisitions are only supported when using the SCXI-1120, SCXI-1120D, or SCXI-1121 modules in parallel mode. Chapter 14, *SCXI Hardware*, describes how the SCXI functions are used to set up the SCXI modules for a data acquisition to be performed by a DAQ device.

**Note** Refer to the Set\_DAQ\_Device\_Info function in the *NI-DAQ Function Reference* Online Help or the Set\_DAQ\_Device\_Info.vi in the LabVIEW DAQ Online Reference for information on data transfer modes.

### Lab and 1200 Devices Data Acquisition Timing

Timing for data acquisition can be performed by the two onboard 8253 Counters/Timers or externally. Each 8253 Counter/Timer has three independent 16-bit counters/timers.

- Counter A0 is a sample-interval counter reserved for data acquisition.

- Counter A1 is a sample counter reserved for data acquisition.

- Counter A2 is an update-interval counter reserved for waveform generation.

- Counter B0 is used for extending the timebase for data acquisition or waveform generation when the interval between samples or updates is greater than 65,535.

- Counter B1 is available for general-purpose counting functions. However, it is reserved during data acquisition interval scanning.

- Counter B2 is available for general-purpose counting functions.

M

Data acquisition timing involves the following timing signals:

- A *start trigger* is an edge-triggered signal that initiates a data acquisition sequence. You can supply a trigger pulse either externally through the I/O connector EXTTRIG input or from software control. You can enable a hardware start trigger by calling the DAQ function DAQ\_Config or specifying trigger mode in the AI\_Start.vi or AI\_Trigger\_Config.vi.

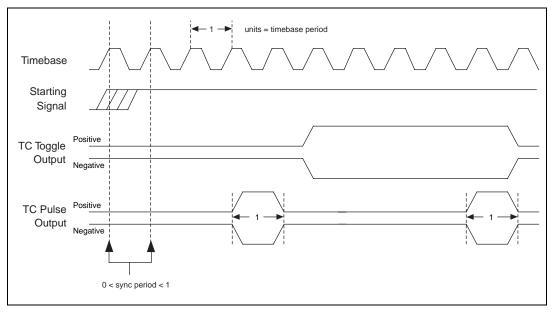

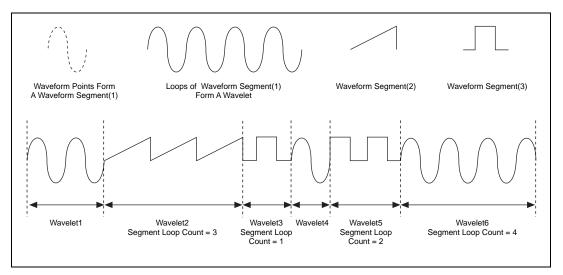

- A *conversion pulse* is a signal that generates a pulse once every sample interval, causing an A/D conversion to be initiated. This signal can be generated by the onboard, programmable sample-interval clock supplied by the 8253 Counter/Timer on the Lab and 1200 device, or can be supplied externally through the I/O connector EXTCONV\* input. You can select external conversion pulses by calling DAQ\_Config. If you do not want to use external conversion pulses, you should disconnect the EXTCONV\* pin on the I/O connector to prevent extra conversions.